电子发烧友网报道(文/黄晶晶)尽管当前AI训练主要采用GPU+HBM的方案,不过一些新的技术仍然希望进一步打破存储数据传输带来的瓶颈问题。最近,NEO半导体宣布开发其3D X-AI芯片技术,旨在取代当前高带宽内存(HBM)中的DRAM芯片,通过在3D DRAM中实现AI处理来解决数据总线问题。

通常来说,当前的 AI芯片架构将数据存储在高带宽内存中,并通过数据总线将数据传输到 GPU 以执行 AI算法(数学计算)。这种架构效率低下,数据总线会导致长时间延迟和高功耗。

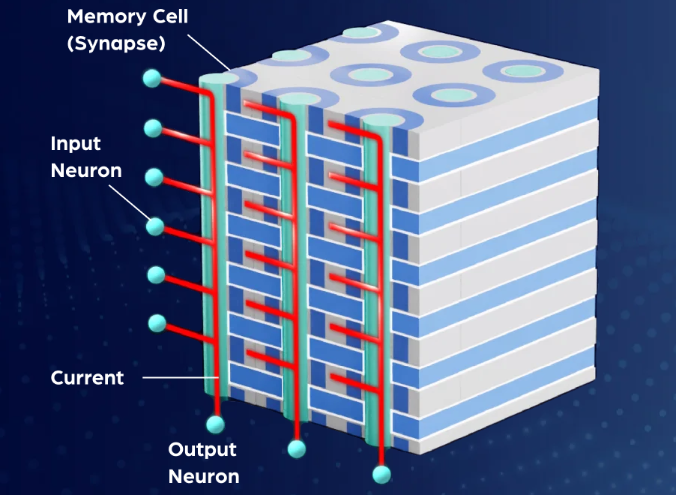

而3D X-AI使用存储单元来模拟神经网络中的突触。它支持在同一芯片中进行数据存储和人工智能操作。存储在存储单元中的数据直接用于生成神经网络的输出,而不进行任何数学计算,从而大大提高人工智能性能并显著节省能源。

来源:NEO半导体官网

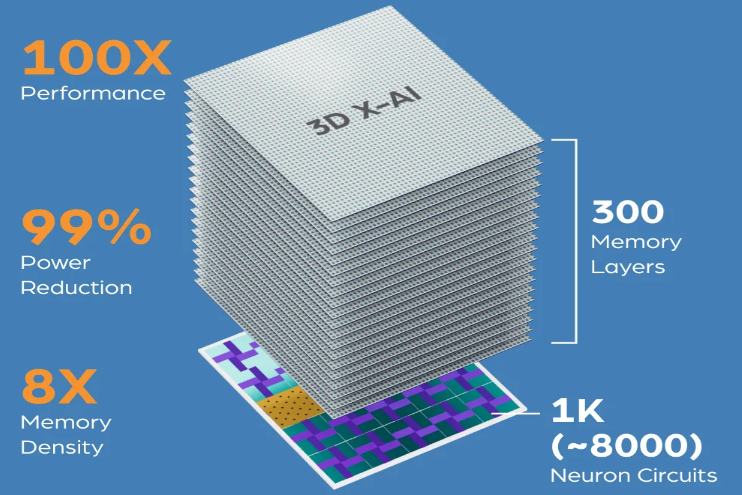

3D X-AI芯片是一种具有AI处理能力的3D DRAM在同一芯片中,它底部有一个神经元电路层,顶部有300层存储单元,容量为128 GB。这种创新的芯片可以将人工智能芯片的性能提高100倍,并将功耗降低99%。它具有8倍更高的密度,非常适合存储大型语言模型(LLM),用于生成式人工智能应用程序,如Chat GPT,Gemini和CoPilot。

来源:NEO半导体官网

NEO半导体介绍,采用NEO的3D X-AI技术的人工智能芯片可实现,100X性能加速:包含8000个神经元电路,可在3D内存中执行A1处理;99%功耗降低:将数据传输到GPU进行计算的需求最小化,从而减少数据总线产生的功耗和热量;8X内存密度:包含300个内存层,允许存储更大的AI模型。据NEO估计,每个芯片可支持高达10 TB/s的AI处理吞吐量。使用12个3D X- AI 芯片堆叠HBM封装可实现120 TB/s处理吞吐量,性能提高100X。

这里的3D DRAM也是NEO半导体的研发方向之一。与水平放置存储单元的传统DRAM不同,3D DRAM垂直堆叠存储单元大大增加单位面积的存储容量并提高效率,成为下一代DRAM关键发展方向。

NEO表示,动态随机存取存储器(DRAM)用于支持处理器,使DRAM在电子设备中的使用更加普遍。然而,处理器速度的增长速度比多代内存速度更快,由此产生的“性能差距”逐年扩大。像云数据中心这样的功耗敏感环境越来越依赖更高功率的处理器来满足性能要求,但这会减少可用于内存的功率。

采用X-DRAM架构可以降低功耗,降低延迟,并增加吞吐量,以克服使用传统DRAM时遇到的这些和其他挑战。这为商业系统(例如服务器)提供了更高的性能,为移动设备(例如智能手机)提供了更长的电池寿命,为边缘计算设备(例如路由器)提供了更多的功能,并为物联网对象(例如网关)提供了新的部署选项。

3D X-DRAM的单元阵列结构类似于3D NAND Flash,采用了FBC(无电容器浮体单元)技术,它可以通过添加层掩模形成垂直结构,从而实现高良率、低成本和显著的密度提升。NEO表示, 3D X-DRAM 技术可以生产230层的128Gbit DRAM 芯片,是当前 DRAM 密度的八倍。近年来,SK海力士、三星电子、美光等存储厂商都在进行3D DRAM技术的研发,以期满足于AI浪潮下对高性能、大容量内存的需求。

-

AI芯片

+关注

关注

17文章

1797浏览量

34572

发布评论请先 登录

相关推荐

2.5D/3D封装技术升级,拉高AI芯片性能天花板

紫光展锐助力全球首款AI裸眼3D手机发布

中兴通讯与中国移动发布全球首创AI裸眼3D新品,引领3D科技新浪潮

三星已成功开发16层3D DRAM芯片

银牛微电子:集3D视觉感知、AI及SLAM为一体的3D空间计算芯

3D DRAM进入量产倒计时,3D DRAM开发路线图

Stability AI推出全新Stable Video 3D模型

AI引领存储市场变革 HBM与DDR5需求暴增

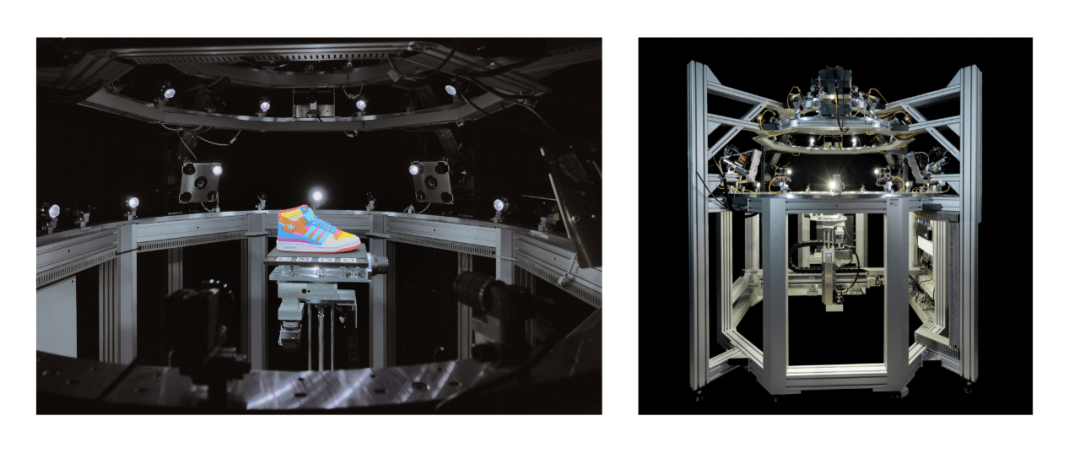

阿迪达斯与 Covision Media 使用 AI 和 NVIDIA RTX 创建逼真的 3D 内容

3D DRAM内嵌AI芯片,AI计算性能暴增

3D DRAM内嵌AI芯片,AI计算性能暴增

评论